Synthese: Difference between revisions

Remi.varenne (talk | contribs) |

Remi.varenne (talk | contribs) |

||

| (16 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

=Neural |

= Neural Processing Unit = |

||

== Description général == |

== Description général == |

||

[[File:NPU.jpeg|300px|right]] |

|||

Une puce d'accélération de réseaux neuronaux (appelé Neural Processing Unit ou NPU) est une forme de microprocesseur. Son but est d'accélérer un réseau de neurones artificiels pour des algorithmes de vision industrielle, de l'automatisation de drones, une amélioration de l'IoT. |

Une puce d'accélération de réseaux neuronaux (appelé Neural Processing Unit ou NPU) est une forme de microprocesseur. Son but est d'accélérer un réseau de neurones artificiels pour des algorithmes de vision industrielle, de l'automatisation de drones, une amélioration de l'IoT. |

||

| ⚫ | |||

Malgré les progrès matériels des dernières décennies, la vitesse de calcul reste un facteur limitant pour les architectures de réseaux neuronaux convolutionnelles ou convolutional neural network (CNN) caractérisées par de nombreux blocs de construction typiquement définis par essais et erreurs. |

Malgré les progrès matériels des dernières décennies, la vitesse de calcul reste un facteur limitant pour les architectures de réseaux neuronaux convolutionnelles ou convolutional neural network (CNN) caractérisées par de nombreux blocs de construction typiquement définis par essais et erreurs. |

||

| Line 14: | Line 13: | ||

Le fait d'accélérer l'unité centrale de traitement ou CPU (Central Processing Unit) a déjà été fait par le passé, avec l'utilisation de cartes vidéos pour les graphiques ou des cartes sons pour l'audio. Pour répondre aux besoins toujours plus important liés à la conception de réseaux neuronaux, des unités matérielles ont été spécialement créées pour celà. |

Le fait d'accélérer l'unité centrale de traitement ou CPU (Central Processing Unit) a déjà été fait par le passé, avec l'utilisation de cartes vidéos pour les graphiques ou des cartes sons pour l'audio. Pour répondre aux besoins toujours plus important liés à la conception de réseaux neuronaux, des unités matérielles ont été spécialement créées pour celà. |

||

== Différentes techniques existantes == |

== Différentes techniques existantes == |

||

=== Arithmétique basse précision === |

=== Arithmétique basse précision === |

||

Les expériences montrent que l'arithmétique en fixed point, qu'on peut aussi appelé arithmétique de faible précision suffit pour la plupart des réseaux. L'arithmétique en fixed point veut dire que les valeurs que l'on trouve sur un réseau seront des valeurs codées sur 8 bits. La deuxième solution existante est l'arithmétique flottante où les valeurs sont des flottants codés sur 28 bits. L'arithmétique basse précision permet de réduire la taille du réseau et donc de réduire le temps d'entrainement du modèle. Plusieurs problèmes sont suffisamment réguliers et adapté à une exécution parallèle et en pipeline. |

Les expériences montrent que l'arithmétique en fixed point, qu'on peut aussi appelé arithmétique de faible précision suffit pour la plupart des réseaux. L'arithmétique en fixed point veut dire que les valeurs que l'on trouve sur un réseau seront des valeurs codées sur 8 bits. La deuxième solution existante est l'arithmétique flottante où les valeurs sont des flottants codés sur 28 bits. L'arithmétique basse précision permet de réduire la taille du réseau et donc de réduire le temps d'entrainement du modèle. Plusieurs problèmes sont suffisamment réguliers et adapté à une exécution parallèle et en pipeline. |

||

| Line 27: | Line 26: | ||

== Différents systèmes existants == |

== Différents systèmes existants == |

||

=== Utilisation des GPU === |

=== Utilisation des GPU === |

||

Les unités de traitement graphiques (ou Graphics Processions Units) sont des processeurs monopuce qui sont conçus pour accélérer les graphiques 3D en temps réel qui sont affichés sur l'interface de l'utilisateur. |

Les unités de traitement graphiques (ou Graphics Processions Units) sont des processeurs monopuce qui sont conçus pour accélérer les graphiques 3D en temps réel qui sont affichés sur l'interface de l'utilisateur. |

||

| Line 41: | Line 40: | ||

=== Utilisation des ASIC === |

=== Utilisation des ASIC === |

||

[[File:Asic.png|300px|right]] |

|||

On a donc noté que les GPU, ainsi que les FPGAs sur lesquels je reviendrai plus bas, permettent d’être beaucoup efficace que l’utilisation unique de CPU pour des tâches d’IA. Il est cependant possible d’être encore plus performant avec une conception toujours plus adaptée à son utilisation avec un "Application-specific integrated circuit" (ASIC). Un ASIC est un circuit intégré spécialisé sur lequel sont regroupées un grand nombre de fonctionnalité adaptées à la tâche future de ce circuit. Ils sont ainsi parfaitement adapté pour l'entrainement de modèle de réseaux neuronaux. |

On a donc noté que les GPU, ainsi que les FPGAs sur lesquels je reviendrai plus bas, permettent d’être beaucoup efficace que l’utilisation unique de CPU pour des tâches d’IA. Il est cependant possible d’être encore plus performant avec une conception toujours plus adaptée à son utilisation avec un "Application-specific integrated circuit" (ASIC). Un ASIC est un circuit intégré spécialisé sur lequel sont regroupées un grand nombre de fonctionnalité adaptées à la tâche future de ce circuit. Ils sont ainsi parfaitement adapté pour l'entrainement de modèle de réseaux neuronaux. |

||

| Line 56: | Line 57: | ||

== Proposition de systèmes existants == |

== Proposition de systèmes existants == |

||

=== Google TPU === |

=== Google TPU === |

||

[[File:TPU.png|100px|thumb|right|Tensor Processing Unit]] |

|||

Le TPU est un ASIC conçu sur mesure suffisamment petit pour s'insérer dans un emplacement de disque dur dans les racks des centres de données de Google. Les ingénieurs de Google disent que le TPU offre une performance par Watt 10 fois plus performante que les solutions déjà commercialisées pour ce qui concerne les tâches de machine learning. Sans surprise, lue TPU est optimisé pour la librairie open-source de machine learning de google, Tenforflow. Il est très souvent utilisé pour l'utilisation de CNN. Il se concentre sur le calcul de valeurs codées sur 8 bits en grande quantité. L'adaptation du TPU à l'arithmétique faible précision a apparemment permis à Google de réaliser des gains importants en matière de conception matérielle. Cette approche a permis à l'entreprise d'éliminer un nombre important de transistors qui auraient autrement été nécessaires pour les opérations courantes. |

Le TPU est un ASIC conçu sur mesure suffisamment petit pour s'insérer dans un emplacement de disque dur dans les racks des centres de données de Google. Les ingénieurs de Google disent que le TPU offre une performance par Watt 10 fois plus performante que les solutions déjà commercialisées pour ce qui concerne les tâches de machine learning. Sans surprise, lue TPU est optimisé pour la librairie open-source de machine learning de google, Tenforflow. Il est très souvent utilisé pour l'utilisation de CNN. Il se concentre sur le calcul de valeurs codées sur 8 bits en grande quantité. L'adaptation du TPU à l'arithmétique faible précision a apparemment permis à Google de réaliser des gains importants en matière de conception matérielle. Cette approche a permis à l'entreprise d'éliminer un nombre important de transistors qui auraient autrement été nécessaires pour les opérations courantes. |

||

=== Intel Nervana NNP === |

=== Intel Nervana NNP === |

||

[[File:NNP.png|300px|thumb|right| Intel Nervana NNP]] |

|||

L'Intel Nervana Neural Network Processor (NNP) est une architecture spécialement conçue pour le deep-learning. L'objectif de cette nouvelle architecture est de fournir la flexibilité nécessaire pour supporter toutes les primitives de deep-learning tout en rendant les composants matériels de base aussi efficaces que possible. L'Intel Nervana NNP a été conçu pour se libérer des limitations imposées par le matériel existant, qui n'était pas explicitement conçu pour l'IA. |

L'Intel Nervana Neural Network Processor (NNP) est une architecture spécialement conçue pour le deep-learning. L'objectif de cette nouvelle architecture est de fournir la flexibilité nécessaire pour supporter toutes les primitives de deep-learning tout en rendant les composants matériels de base aussi efficaces que possible. L'Intel Nervana NNP a été conçu pour se libérer des limitations imposées par le matériel existant, qui n'était pas explicitement conçu pour l'IA. |

||

| Line 72: | Line 77: | ||

=== HiSilicon Kirin 970 === |

=== HiSilicon Kirin 970 === |

||

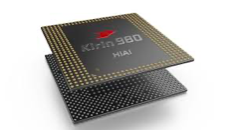

[[File:Kirin.png|300px|thumb|right| Kirin 980]] |

|||

| ⚫ | Huawei suit le même principe qu’Apple avec sa propre puce.Kirin 970 est alimenté par un CPU 8 cœurs et un GPU 12 cœurs de nouvelle génération. La puce regroupe 5,5 milliards de transistors dans une surface de seulement un cm2. La nouvelle figure de proue en terme de NPU de Huawei, le Kirin 970, est la première plate-forme informatique mobile d'IA de HUAWEI dotée d'un NPU dédié. Comparée à un cluster de CPU quadricœur Cortex-A73, la nouvelle architecture de calcul hétérogène de Kirin 970 offre jusqu'à 25 fois plus de performances avec une efficacité 50 fois supérieure. En d'autres termes, le Kirin 970 peut exécuter les mêmes tâches de calcul AI plus rapidement et avec beaucoup moins de puissance. Lors d'un test de reconnaissance d'images de référence, la Kirin 970 a traité 2000 images par minute, ce qui est plus rapide que les autres puces actuel du marché. |

||

| ⚫ | Huawei suit le même principe qu’Apple avec sa propre puce. Kirin 970 est alimenté par un CPU 8 cœurs et un GPU 12 cœurs de nouvelle génération. La puce regroupe 5,5 milliards de transistors dans une surface de seulement un cm2. La nouvelle figure de proue en terme de NPU de Huawei, le Kirin 970, est la première plate-forme informatique mobile d'IA de HUAWEI dotée d'un NPU dédié. Comparée à un cluster de CPU quadricœur Cortex-A73, la nouvelle architecture de calcul hétérogène de Kirin 970 offre jusqu'à 25 fois plus de performances avec une efficacité 50 fois supérieure. En d'autres termes, le Kirin 970 peut exécuter les mêmes tâches de calcul AI plus rapidement et avec beaucoup moins de puissance. Lors d'un test de reconnaissance d'images de référence, la Kirin 970 a traité 2000 images par minute, ce qui est plus rapide que les autres puces actuel du marché. |

||

=== Intel Neural Compute Stick 2 === |

=== Intel Neural Compute Stick 2 === |

||

[[File:NCS2.png|400px|thumb|right|Intel Neural Compute Stick 2]] |

|||

Le Intel Neural Compute Stick 2 (NCS2) est un kit de développement plug and play pour l'intelligence artificielle. Il a été développé pour être utilisé aussi bien sur Ubuntu que Windows et MacOS ainsi qu'avec des prototype avec dispositifs à faible coût tel que le Raspeberry PI*3. Le NCS2 a été conçu pour utilisé les frameworks communs d'intelligence artificielle tel que Tensorflow, Keras ou Pytorch et il fonctionne sans dépendance se trouvant dans le cloud contrairement à la puce d'Apple. |

Le Intel Neural Compute Stick 2 (NCS2) est un kit de développement plug and play pour l'intelligence artificielle. Il a été développé pour être utilisé aussi bien sur Ubuntu que Windows et MacOS ainsi qu'avec des prototype avec dispositifs à faible coût tel que le Raspeberry PI*3. Le NCS2 a été conçu pour utilisé les frameworks communs d'intelligence artificielle tel que Tensorflow, Keras ou Pytorch et il fonctionne sans dépendance se trouvant dans le cloud contrairement à la puce d'Apple. |

||

| Line 96: | Line 105: | ||

* '''Efficacité''' : La puissance du système est une considération clé, de la périphérie au centre de données. Lors de la sélection de solutions d'apprentissage approfondi, l'efficacité énergétique (débit/watt) est un facteur critique à prendre en compte. Les conceptions Intel offrent une excellente efficacité énergétique pour les charges de travail d'apprentissage approfondi. |

* '''Efficacité''' : La puissance du système est une considération clé, de la périphérie au centre de données. Lors de la sélection de solutions d'apprentissage approfondi, l'efficacité énergétique (débit/watt) est un facteur critique à prendre en compte. Les conceptions Intel offrent une excellente efficacité énergétique pour les charges de travail d'apprentissage approfondi. |

||

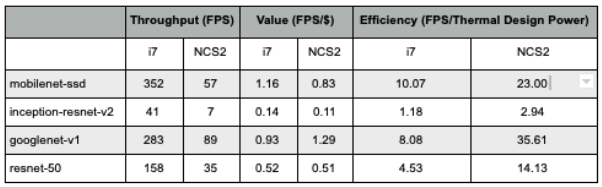

[[File:Résultats NCS2.png|700px|thumb|center]] |

|||

Comme on peut le voir sur le tableau ci dessus, l'ajout d'un NCS2 réduit drastiquement le débit ainsi que les valeurs retournées par les différents modèles. Cependant, on peut remarquer qu'on gagne 2 fois plus d'efficacité avec l'ajout du stick sur une machine ayant un CPU i7. |

|||

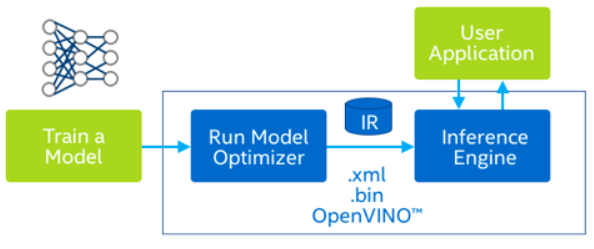

Si on se rapproche un peu plus de l'applicatif, il est possible d'utiliser l'outil OpenVino qui permet aux développeurs de déployer des modèles pré-entrainés de deep-learning à travers du C++ haut level ou avec Python en faisant fonctionner l'API intégré. Cet outil suppose de multiples plateformes Intel. |

Si on se rapproche un peu plus de l'applicatif, il est possible d'utiliser l'outil OpenVino qui permet aux développeurs de déployer des modèles pré-entrainés de deep-learning à travers du C++ haut level ou avec Python en faisant fonctionner l'API intégré. Cet outil suppose de multiples plateformes Intel. |

||

| ⚫ | |||

| ⚫ | A l'intérieur de cet outil se trouve l'optimiseur de modèle qui est un outil de ligne de commande en Python qui importe des modèles créés par les frameworks populaires de deep-learning. Il est capable de fonctionner sur de multiples systèmes d' |

||

| ⚫ | A l'intérieur de cet outil se trouve l'optimiseur de modèle qui est un outil de ligne de commande en Python qui importe des modèles créés par les frameworks populaires de deep-learning. Il est capable de fonctionner sur de multiples systèmes d'exploitaton et retourne des analyses et des ajustements pour une execution optimale sur des dispositifs cibles en utilisant des modèles statiques et entraînés. |

||

On y retrouve aussi le moteur d'inférence qui utilise une API commune pour délivrer des solutions d'inférence sur la plateforme choisie: CPU, GPU, VPU ou FPGA. Il fonctionne sur différentes couches avec différentes (comme par exemple un GPU and des couches sélectionnées sur un CPU). Il implémente des couches customizes sur un CPU tout en exécutant la topologie restante sur un GPU - sans avoir à réécrire les couches personnalisées. Il peut aussi optimiser les charges de travail (analyse des graphiques de calcul, ordonnancement et compression des modèles) pour le matériel cible grâce à une solution de notation conviviale intégrée, profiter de la nouvelle exécution asynchrone pour améliorer les performances de la fréquence d'images tout en limitant les cycles perdus , et utiliser une API C++ ou Python pratique pour travailler sur les fichiers IR et optimiser l'inférence. |

On y retrouve aussi le moteur d'inférence qui utilise une API commune pour délivrer des solutions d'inférence sur la plateforme choisie: CPU, GPU, VPU ou FPGA. Il fonctionne sur différentes couches avec différentes (comme par exemple un GPU and des couches sélectionnées sur un CPU). Il implémente des couches customizes sur un CPU tout en exécutant la topologie restante sur un GPU - sans avoir à réécrire les couches personnalisées. Il peut aussi optimiser les charges de travail (analyse des graphiques de calcul, ordonnancement et compression des modèles) pour le matériel cible grâce à une solution de notation conviviale intégrée, profiter de la nouvelle exécution asynchrone pour améliorer les performances de la fréquence d'images tout en limitant les cycles perdus , et utiliser une API C++ ou Python pratique pour travailler sur les fichiers IR et optimiser l'inférence. |

||

== Références == |

|||

* [https://fr.wikipedia.org/wiki/Puce_d%27accélération_de_réseaux_de_neurones#cite_note-28 Neural Processing Unit] |

|||

* [https://www.movidius.com/ Le Intel Movidius, un dongle USB conçu pour le "vision processing"] |

|||

* [https://papers.nips.cc/paper/4824-imagenet-classification-with-deep-convolutional-neural-networks.pdf ImageNet Classification with deep convolutional neural networks] |

|||

* [https://arxiv.org/pdf/1102.0183.pdf High-Performance Neural Networks for Visual Object Classification] |

|||

* [https://insidehpc.com/2017/06/inspurs-unveils-gx4-ai-accelerator/ Inspur unveils GX4 AI accelerator] |

|||

* [https://www.researchgate.net/publication/15149042_Designing_a_connectionist_network_supercomputer Designing a connectionist network supercomputer] |

|||

* [https://www.researchgate.net/publication/220851449_Video_Processing_and_Retrieval_on_Cell_Processor_Architecture Video processing and retrieval on cell processor architecture] |

|||

* [https://software.intel.com/en-us/articles/improving-the-compute-performance-of-video-processing-software-using-avx-advanced-vector-extensions-instructions Improving the compute performance of video processing software using Intel advanced vector extensions (Intel AVX) instructions] |

|||

* [https://hal.inria.fr/inria-00112631/document High Performance Convolutional Neural Networks for Document Processing High performance convolutional neural networks for document processing] |

|||

* [https://devblogs.nvidia.com/how-nvlink-will-enable-faster-easier-multi-gpu-computing/ How NVLink will enable faster, easier multi-GPU computing] |

|||

* [https://www.nextplatform.com/2016/08/23/fpga-based-deep-learning-accelerators-take-asics/ FPGA based deep-learning accelerator take on asics] |

|||

* [https://www.nextplatform.com/2015/08/27/microsoft-extends-fpga-reach-from-bing-to-deep-learning/ Microsoft extends FPGA reach from Bing to deep learning] |

|||

* [https://www.microsoft.com/en-us/research/wp-content/uploads/2016/02/CNN20Whitepaper.pdf Accelerating deep convolutional neural networks using specialized hardware] |

|||

* [http://techreport.com/news/30155/google-boosts-machine-learning-with-its-tensor-processing-unit Google boosts machine learning with its Tensor Processing Unit] |

|||

* [https://www.sciencedaily.com/releases/2016/02/160203134840.htm Chip could bring deep learning to mobile devices] |

|||

* [https://arxiv.org/pdf/1502.02551.pdf deep learning with limited numerical precision] |

|||

* [https://www.intel.ai/intel-nervana-neural-network-processors-nnp-redefine-ai-silicon/ Intel Nervana neural network processors redefine AI Silicon] |

|||

* [https://www.huawei.com/en/press-events/news/2017/9/mobile-ai-ifa-2017 Huawei reveals the future of mobile AI at IFA 2017] |

|||

* [https://www.extremetech.com/extreme/187612-ibm-cracks-open-a-new-era-of-computing-with-brain-like-chip-4096-cores-1-million-neurons-5-4-billion-transistors IBM cracks open a new era of computing with brain-like chip: 4096 cores, 1 million neurons, 5.4 billion transistors] |

|||

* [https://newsroom.intel.com/editorials/intels-new-self-learning-chip-promises-accelerate-artificial-intelligence/ Intel’s new self-learning chip promises to accelerate AI] |

|||

Latest revision as of 10:49, 6 January 2020

Neural Processing Unit

Description général

Une puce d'accélération de réseaux neuronaux (appelé Neural Processing Unit ou NPU) est une forme de microprocesseur. Son but est d'accélérer un réseau de neurones artificiels pour des algorithmes de vision industrielle, de l'automatisation de drones, une amélioration de l'IoT.

Malgré les progrès matériels des dernières décennies, la vitesse de calcul reste un facteur limitant pour les architectures de réseaux neuronaux convolutionnelles ou convolutional neural network (CNN) caractérisées par de nombreux blocs de construction typiquement définis par essais et erreurs.

En effet, l'amélioration de la performance globale du système due à l'accélération d'une partie du système (par exemple, un calcul plus rapide via le parallélisme) est limitée par la fraction du travail qui n'est pas accélérée (par exemple, le code série). Par exemple, si 90% d'une tâche est accélérée à l'infini, la tâche globale n'est effectuée que dix fois plus vite.

La plupart des systèmes utilisés utilise une conception multicoeur pour de différentes utilisations tel que l'arithmétique basse précision ou l'architecture en flux de données. Je reviendrai sur ces techniques plus tard.

Le fait d'accélérer l'unité centrale de traitement ou CPU (Central Processing Unit) a déjà été fait par le passé, avec l'utilisation de cartes vidéos pour les graphiques ou des cartes sons pour l'audio. Pour répondre aux besoins toujours plus important liés à la conception de réseaux neuronaux, des unités matérielles ont été spécialement créées pour celà.

Différentes techniques existantes

Arithmétique basse précision

Les expériences montrent que l'arithmétique en fixed point, qu'on peut aussi appelé arithmétique de faible précision suffit pour la plupart des réseaux. L'arithmétique en fixed point veut dire que les valeurs que l'on trouve sur un réseau seront des valeurs codées sur 8 bits. La deuxième solution existante est l'arithmétique flottante où les valeurs sont des flottants codés sur 28 bits. L'arithmétique basse précision permet de réduire la taille du réseau et donc de réduire le temps d'entrainement du modèle. Plusieurs problèmes sont suffisamment réguliers et adapté à une exécution parallèle et en pipeline.

Les unités de calcul utilisant des valeurs en fixed-point sont généralement plus rapides et consomment beaucoup moins de ressources matérielles et de puissance que les unités de calculs à valeurs flottantes. La plus petite empreinte logique des circuits arithmétiques en fixed-point permettrait l'instanciation de beaucoup plus d'unités de ce type pour une surface et un budget de puissance donnés. De plus, la représentation de données de faible précision réduit l'empreinte mémoire, ce qui permet aux modèles de plus grande taille de s'adapter à la capacité mémoire donnée et de réduire les besoins en bande passante. Cumulativement, cela pourrait permettre d'améliorer considérablement le parallélisme au niveau des données.

Parallelisation

L'accent mis dans la parallelisation dans les GPU conduit à l'optimisation du débit, en masquant plutôt qu'en minimisant la latence. La prise en charge de milliers de threads garantit un partage des tâches face aux dépendances de données afin de maintenir les performances à un pourcentage élevé.

Les CPU modernes permettent des "instructions level parallelism" (ILP), autrement dit, ils permettent d'exécuter des instructions en parallèle.

Différents systèmes existants

Utilisation des GPU

Les unités de traitement graphiques (ou Graphics Processions Units) sont des processeurs monopuce qui sont conçus pour accélérer les graphiques 3D en temps réel qui sont affichés sur l'interface de l'utilisateur.

Les GPUs sont utilisées principalement pour la manipulation d'images, or ceci est également grandement utilisé dans l'intelligence artificielle. En effet, nous pouvons retrouver de grandes similarités dans les formules mathématiques utilisées das les réseaux neuronaux ainsi que la manipulation d'images. Nous pouvons donc dans les deux cas faire de la parallelisation de calculs compliqués utilisant des matrices.

Les études actuelles sur la conception et la configuration des GPUs ont permis d'obtenir une mémoire dédiée plus importante, une bande passante plus large vers la mémoire graphique et un parallélisme interne accru. De plus, les GPUs actuels sont sont toujours plus programmables.

Avec l'introduction de la programmabilité, les GPUs ont gagné suffisamment de flexibilité pour être utilisé dans des applications non graphiques. De plus, l'architecture d'accès en parallèle aux données des GPU offre des gains de performance considérables par rapport aux CPU pour les applications à forte intensité de calcul. Des extensions aux algorithmes graphiques alternatifs et aux problèmes de calcul scientifique ont été explorées dans un certain nombre de cas.

Les GPU sont ainsi devenues beaucoup plus populaires pour accélérer l'entrainement de réseaux neuronaux et cela ne cesse de s'améliorer. Ils sont très efficaces pour l'apprentissage et l'inférence dans des dispositifs de plus en plus autonomes comme pour les véhicules automatiques.

Une étude a fait un entrainement de modèles sur de multiples GPU. Un GTX 580 GPU a un espace limité de mémoire, ce qui limite la taille maximale des réseaux qui peuvent être entrainer dessus. Ils ont réparti le réseau sur 2 GPU. Les GPUs actuels sont particulièrement adaptés pour la parallelisation entre GPUs, ils sont donc capable de lire et d'écrire sur la mémoire des différents GPUs, sans passer par la machine hôte. Le schéma de parallelisation employé met la moitié des neurones sur chaque GPU.

Utilisation des ASIC

On a donc noté que les GPU, ainsi que les FPGAs sur lesquels je reviendrai plus bas, permettent d’être beaucoup efficace que l’utilisation unique de CPU pour des tâches d’IA. Il est cependant possible d’être encore plus performant avec une conception toujours plus adaptée à son utilisation avec un "Application-specific integrated circuit" (ASIC). Un ASIC est un circuit intégré spécialisé sur lequel sont regroupées un grand nombre de fonctionnalité adaptées à la tâche future de ce circuit. Ils sont ainsi parfaitement adapté pour l'entrainement de modèle de réseaux neuronaux.

Etant donné que cette pièce est faite sur mesure, c’est interessant de commander des ASICs en grande quantité pour rentabiliser le coût initial important.

Utilisation des FPGA

Il est pour l’instant difficile de concevoir du matériel sur mesure car les frameworks d’apprentissage approfondi continuent d’évoluer. Heureusement, ils utilisent des "field-programmable gate array" (FPGA) qui sont des dispositifs reconfigurables qui permettent de faire facilement évoluer les frameworks, mais également les logiciels et le matériel.

Les FPGAs sont des circuits logique programmable qui sont des circuits intégrés qui peuvent être reprogrammés après sa fabrication. Ils sont connectés de manières réversibles par programmation pour réaliser des fonctions numériques désirées. On peut donc utiliser une même puce pour de nombreux usages différents.

On utilise les FPGAs pour de multiples applications numériques ainsi que pour le prototypage. Si l’on comparait les FPGAs aux ASICs, on pourrait dire que les FGPAs sont en général plus lents, plus chers à la pièce et qu’ils sont beaucoup coutant en terme d’énergie. Cependant, ils ont également de nombreux avantages. En effet, la production de ces pièces est assez rapide car ce sont des pièces standardisées et que le temps de conception est court car des fonctions de base comme la reconfiguration autorise des normes de production moins strictes. Enfin, pour de petites quantités, le cout des FPGAs est plus faible.

On peut retrouver de nombreuses compagnies s’intéresser aux FGPAs tel que Microsoft qui souhaitent les utiliser pour accélérer l’inférence ou Intel qui veut intégrer les FPGAs dans les CPUs des serveurs pour accélérer l’intelligence artificielle.

Proposition de systèmes existants

Google TPU

Le TPU est un ASIC conçu sur mesure suffisamment petit pour s'insérer dans un emplacement de disque dur dans les racks des centres de données de Google. Les ingénieurs de Google disent que le TPU offre une performance par Watt 10 fois plus performante que les solutions déjà commercialisées pour ce qui concerne les tâches de machine learning. Sans surprise, lue TPU est optimisé pour la librairie open-source de machine learning de google, Tenforflow. Il est très souvent utilisé pour l'utilisation de CNN. Il se concentre sur le calcul de valeurs codées sur 8 bits en grande quantité. L'adaptation du TPU à l'arithmétique faible précision a apparemment permis à Google de réaliser des gains importants en matière de conception matérielle. Cette approche a permis à l'entreprise d'éliminer un nombre important de transistors qui auraient autrement été nécessaires pour les opérations courantes.

Intel Nervana NNP

L'Intel Nervana Neural Network Processor (NNP) est une architecture spécialement conçue pour le deep-learning. L'objectif de cette nouvelle architecture est de fournir la flexibilité nécessaire pour supporter toutes les primitives de deep-learning tout en rendant les composants matériels de base aussi efficaces que possible. L'Intel Nervana NNP a été conçu pour se libérer des limitations imposées par le matériel existant, qui n'était pas explicitement conçu pour l'IA.

La multiplication des matrices et les convolutions sont au cœur du deep-learning. Ces calculs sont différents de ce qui se fait généralement puisque les opérations et les mouvements de données sont largement connus a priori. Pour cette raison, le Nervana NNP d'Intel n'a pas de hiérarchie de cache standard et la mémoire sur puce est gérée directement par le logiciel. Une meilleure gestion de la mémoire permet à la puce d'atteindre des niveaux élevés d'utilisation de la quantité massive de calcul sur chaque puce. Cela se traduit par un temps de formation plus rapide pour les modèles de Deep Learning.

Conçu avec des interconnexions à haut débit sur et hors puce, le NNP Intel Nervana permet un transfert de données bidirectionnel massif. Un des objectifs de la conception était de parvenir à un véritable parallélisme des modèles où les paramètres des réseaux neuronaux sont répartis sur plusieurs puces. Ainsi, plusieurs puces agissent comme une seule grande puce virtuelle qui peut accueillir des modèles plus importants, ce qui permet aux clients de tirer davantage d'informations de leurs données.

Movidius Myriad 2

Movidius Myriad 2 est un accélérateur VLIW AI à multicoeur qui est complété par des unités de fonctions vidéos fixes. Un "very long instruction word" (VLIW) représente une famille d’ordinateurs qui possèdent un processeur à mot d’instruction très long (en général supérieur à 128 bits). On peut associé cette technologie à la gestion du pipeline d’exécution d’un processeur dans les compteurs. Elle va fournir des instructions longue correspondant à plusieurs courtes instructions.

Neural Engine

Neural Engine est un noyau d'accélérateur d'intelligence artificielle placé au sein du SOC A11 Bionic d'Apple. C’est la puce qu’utilise Apple à partir de son iPhone X pour ses fonctionnalités de reconnaissance faciale et réalité augmenté. Elle est composée d’un pair de coeurs dédiés à l’utilisation d’algorithmes spécifiques au machine learning (ML). Il peut faire plus de 600 milliards d’opération par seconde pour aider aux tâches d’intelligence artificielle (Il est cependant léger de donner uniquement son nombre d’opérations par seconde pour représenter l’efficacité de cette puce).

HiSilicon Kirin 970

Huawei suit le même principe qu’Apple avec sa propre puce. Kirin 970 est alimenté par un CPU 8 cœurs et un GPU 12 cœurs de nouvelle génération. La puce regroupe 5,5 milliards de transistors dans une surface de seulement un cm2. La nouvelle figure de proue en terme de NPU de Huawei, le Kirin 970, est la première plate-forme informatique mobile d'IA de HUAWEI dotée d'un NPU dédié. Comparée à un cluster de CPU quadricœur Cortex-A73, la nouvelle architecture de calcul hétérogène de Kirin 970 offre jusqu'à 25 fois plus de performances avec une efficacité 50 fois supérieure. En d'autres termes, le Kirin 970 peut exécuter les mêmes tâches de calcul AI plus rapidement et avec beaucoup moins de puissance. Lors d'un test de reconnaissance d'images de référence, la Kirin 970 a traité 2000 images par minute, ce qui est plus rapide que les autres puces actuel du marché.

Intel Neural Compute Stick 2

Le Intel Neural Compute Stick 2 (NCS2) est un kit de développement plug and play pour l'intelligence artificielle. Il a été développé pour être utilisé aussi bien sur Ubuntu que Windows et MacOS ainsi qu'avec des prototype avec dispositifs à faible coût tel que le Raspeberry PI*3. Le NCS2 a été conçu pour utilisé les frameworks communs d'intelligence artificielle tel que Tensorflow, Keras ou Pytorch et il fonctionne sans dépendance se trouvant dans le cloud contrairement à la puce d'Apple.

Il peut notamment deployer des CNN sur des applications consommant peu d'énergie ce qui requiert un fonctionnement en temps réel. L'avantage du NCS2 est qu'il va accélérer le déploiement de modèle de réseaux neuronaux sur les plateformes Intel avec l'outil associé "deep-learning deployment toolkit" (DLPT).

On peut facilement le prendre en main, avec des modèles pré-entrainés, des librairies de fonctions et un noyau pré-optimisé pour une livraison du produit utilisant l'IA rapide.

Il est capable de supporter le calcul hétérogène à travers d'autres accélérateurs comme des GPU ou un FPGA en utilisant une API commune. En effet, il pourra maitriser la performance des accélérateurs basé sur une technologie Intel.

L’intel NCS2 est un Movidius Myriad X placé sur une machine ayant le un CPU i7. Les compteurs d’intel peuvent ou ne peuvent pas être optimiser au même degré pour les micro-processeurs qui ne sont pas d’Intel. L’organisation des dépendances des micro-processeurs est prévue pour l’utilisation des microprocesseurs d’Intel.

Un pipeline de vision par ordinateur typique avec deep-learning peut être constitué de fonctions de vision régulières (comme le prétraitement d'images) et d'un réseau neuronal convolutif (CNN). Les graphiques CNN sont accélérés sur le FPGA ou sur les Intel Movidius Neural Compute Sticks (NCS), tandis que le reste des pipelines de vision fonctionnent sur un processeur hôte.

Les tests passés ont démontré une nette amélioration des performances sur plusieurs modèles de réseaux neuronaux publics avec un développement du modèle sur les CPU, GPU et FPGA d'Intel.

Pour étudier les résultats, ils ont utilisé certaines mesures pour étudier la performance du NCS2 :

- Débit : mesure le nombre d'inférences livrées à l'intérieur d'un seuil de latence (par exemple, le nombre d'images par seconde). Lors du déploiement d'un système avec inférence d'apprentissage profond, sélectionnez le débit qui offre le meilleur compromis entre latence et puissance pour le prix et les performances qui répondent à vos exigences.

- Valeur : Bien que le débit soit important, ce qui est plus critique dans le déploiement de l'AI de pointe est l'efficacité de la performance ou la performance par coût. La performance des applications en termes de débit par dollar de système est la meilleure mesure de la valeur.

- Efficacité : La puissance du système est une considération clé, de la périphérie au centre de données. Lors de la sélection de solutions d'apprentissage approfondi, l'efficacité énergétique (débit/watt) est un facteur critique à prendre en compte. Les conceptions Intel offrent une excellente efficacité énergétique pour les charges de travail d'apprentissage approfondi.

Comme on peut le voir sur le tableau ci dessus, l'ajout d'un NCS2 réduit drastiquement le débit ainsi que les valeurs retournées par les différents modèles. Cependant, on peut remarquer qu'on gagne 2 fois plus d'efficacité avec l'ajout du stick sur une machine ayant un CPU i7.

Si on se rapproche un peu plus de l'applicatif, il est possible d'utiliser l'outil OpenVino qui permet aux développeurs de déployer des modèles pré-entrainés de deep-learning à travers du C++ haut level ou avec Python en faisant fonctionner l'API intégré. Cet outil suppose de multiples plateformes Intel.

A l'intérieur de cet outil se trouve l'optimiseur de modèle qui est un outil de ligne de commande en Python qui importe des modèles créés par les frameworks populaires de deep-learning. Il est capable de fonctionner sur de multiples systèmes d'exploitaton et retourne des analyses et des ajustements pour une execution optimale sur des dispositifs cibles en utilisant des modèles statiques et entraînés.

On y retrouve aussi le moteur d'inférence qui utilise une API commune pour délivrer des solutions d'inférence sur la plateforme choisie: CPU, GPU, VPU ou FPGA. Il fonctionne sur différentes couches avec différentes (comme par exemple un GPU and des couches sélectionnées sur un CPU). Il implémente des couches customizes sur un CPU tout en exécutant la topologie restante sur un GPU - sans avoir à réécrire les couches personnalisées. Il peut aussi optimiser les charges de travail (analyse des graphiques de calcul, ordonnancement et compression des modèles) pour le matériel cible grâce à une solution de notation conviviale intégrée, profiter de la nouvelle exécution asynchrone pour améliorer les performances de la fréquence d'images tout en limitant les cycles perdus , et utiliser une API C++ ou Python pratique pour travailler sur les fichiers IR et optimiser l'inférence.

Références

- Neural Processing Unit

- Le Intel Movidius, un dongle USB conçu pour le "vision processing"

- ImageNet Classification with deep convolutional neural networks

- High-Performance Neural Networks for Visual Object Classification

- Inspur unveils GX4 AI accelerator

- Designing a connectionist network supercomputer

- Video processing and retrieval on cell processor architecture

- Improving the compute performance of video processing software using Intel advanced vector extensions (Intel AVX) instructions

- High Performance Convolutional Neural Networks for Document Processing High performance convolutional neural networks for document processing

- How NVLink will enable faster, easier multi-GPU computing

- FPGA based deep-learning accelerator take on asics

- Microsoft extends FPGA reach from Bing to deep learning

- Accelerating deep convolutional neural networks using specialized hardware

- Google boosts machine learning with its Tensor Processing Unit

- Chip could bring deep learning to mobile devices

- deep learning with limited numerical precision

- Intel Nervana neural network processors redefine AI Silicon

- Huawei reveals the future of mobile AI at IFA 2017

- IBM cracks open a new era of computing with brain-like chip: 4096 cores, 1 million neurons, 5.4 billion transistors

- Intel’s new self-learning chip promises to accelerate AI