EA2013/xeon phi

Motivations

Même si les processeurs deviennent de plus en plus puissants, leur performances sont

limitées. Le plus rapide des processeurs actuels possède 6 unités de traitement pouvant

fonctionner jusqu’à environ 4Ghz et est spécialisé dans le traitement d’instructions séquentielles.

Dans le cas où le programmeur a besoin de faire exécuter la même tâche sur un

grand ensemble de données, il est plus performant de paralléliser le calcul pour gagner

en puissance plutôt que d’augmenter la fréquence de fonctionnement. En effet, pour

gagner en puissance sur une seule unit ́e de traitement il est nécessaire d’augmenter

la fréquence et donc d’augmenter la tension de fonctionnement. Par effet Joule, le

processeur chauffe donc beaucoup plus jusqu’au point ou il n'est plus possible de le

refroidir efficacement.

Différentes approches

SISD (Single Instruction on Single Data)

SISD est une architecture matérielle dans laquelle un seul processeur exécute un seul flot d'instruction sur des données résidant dans une seule mémoire. Il n'y a donc aucune parallélisation.

SIMD (Single Instruction on Multiple Data)

SIMD est une architecture ou il est possible d'executer simultanément la même instruction sur plusieurs données. Il ne faut pas confondre SIMD et multi-coeur. En effet, dans une architecture multi-coeurs les traitements des différents cœurs sont indépendants alors que dans le paradigme SIMD, c'est exactement la même instruction qui est executée sur les différentes données.

La plupart du temps, ce paradigme est mis en œuvre en utilisant la vectorisation (cf plus bas).

MIMD (Multiple Instructions on Multiple Data)

MIMD est en fait l'intégration de plusieurs puces ayant l'architecture SIMD dans une seule. Tous les processeurs multicores du marché sont des puces MIMD

Vectorisation

Contrairement a une implémentation scalaire, qui traite une seule paire d'opérandes à la fois, une implémentation vectorielle traite une opération sur plusieurs paires d'opérandes à la fois. Le terme vient de la convention de mettre les opérandes dans des vecteurs ou des matrices.

Exemple : calculer les carrés des entiers d'un vecteur A et ls stocker dans un vecteur B..

Dans une approche classique (scalaire), les cases du vecteur 1 sont traitées une par une.

for (int a=0 ; i<A.length ; i++){

B[i] = A[i] * A[i] ;

}

Dans une approche SISD, il faudrait A.length tours de boucle pour terminer le calcul.

La vectorisation permet de calculer, via l'utilisation de registres de 128, 256 ou 512 bits, de calculer 4, 8 ou 16 cases du vecteur en un coup.

Il est toujours possible de paralléliser les calculs via plusieurs threads si il n'y a pas de dépendances de données. Dans le cas de l'utilisation d'un Core i5 de la génération Haswell (par exemple), les meilleures performances sont obtenues en parallélisant les calculs sur 4 threads (le processeur possède 4 cœurs physiques, sans Hyperthreading) et en faisant utilisation des instruction AVX2 permettant de calculer 8 cases en même temps par cœur. Il est donc possible de remplir le tableau par coup de 32 cases.

Xeon Phi

Presentation

Xeon Phi est le nom commercial utilisa par Indel pour désigner une famille de multiprocesseurs basés sur l'architecture MIC (Many Integrated Core architecture).

Cette architecture se base sur l'intégration d'un grand nombre (57-61) de cœurs x86 légèrement revus pour intégrer des registres de 512 bits permettant une vectorisation optimisée des instructions ainsi qu'une technologie Hyperthreading améliorée permettant la gestion matérielle simultanée de 4 threads par cœurs (contrairement a 2 dans les processeurs classiques exploitant cette technologie).

Le Xeon phi possède donc 240 cœurs logiques comme le montre la commande 'cat /proc/cpuinfo'

processor : 239

vendor_id : GenuineIntel

cpu family : 11

model : 1

model name : 0b/01

stepping : 3

cpu MHz : 1052.630

cache size : 512 KB

physical id : 0

siblings : 240

core id : 59

cpu cores : 60

apicid : 239

initial apicid : 239

fpu : yes

fpu_exception : yes

cpuid level : 4

wp : yes

flags : fpu vme de pse tsc msr pae mce cx8 apic mtrr mca pat fxsr ht syscall nx lm rep_good nopl lahf_lm

bogomips : 2114.08

clflush size : 64

cache_alignment : 64

address sizes : 40 bits physical, 48 bits virtual

power management:

Les Xeon Phi se présentent sous la forme de cartes d'extension Pci-Express (à la manière des cartes graphiques). Leur consommation maximale en charge est d'approximativement 280W et elles peuvent déployer une puissance de calcul théorique de 2400 Gflops (milliard d'opérations a virgule flottante par seconde).

Architecture mémoire et réseau d'interconnexion

Tous les cœurs de la carte se partagent une mémoire de 8 à 16 Go, distincte de la mémoire principale de l'ordinateur. De par le fait d'un grand nombre de cœur et de l'utilisation de la vectorisation sur de très grands vecteurs, L'utilisation d'une architecture mémoire classique n'est pas envisageable pour des questions de performance.

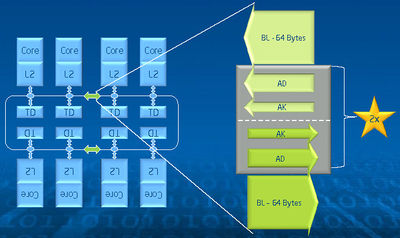

Le réseau d'interconnexion est un anneau bidirectionnel composé de :

- un bus de données de 64 octets

- un bus d'adresses plus petit d'environ 40 bits

- un bus encore plus petit pour l'acquittement des messages

Grâce a cette architecture, le débit théorique pouvant être obtenu approche les 320 Go/s.

Compilation du programme

Le xeon phi etant un systeme a part entière (processeur, mémoire, etc.), compiler n'est pas aussi simple qu'il n'y paraît. Il faut en effet, faire de la cross-compilation c'est à dire compiler pour une achitecture A à partir d'un ordinateur tournant sur une architecture B. Cela sous-entend non-seulement de compiler ses sources correctement, mais oblige également à recompiler spécialement pour le Xeon Phi toutes les librairies utilisées.

Le compilateur a utiliser est le compilateur intel. L'utilisation du flag -mmic indique que l'architecture de destination est un Xeon phi.

icc -O3 -mmic program.c -o program

Transfert et execution du programme

Le Xeon phi se comporte, pour la machine hôte, comme un autre ordinateur accessible via ssh a travers l'interface mic0.

Deux solutions s'offrent à nous pour executer le programme précédemment compilé :

- Le transférer dans la mémoire du Xeon Phi via sftp

- Partager un dossier de la machine hôte et s'y connecter à partir du xeon phi

Dans le cas ou les données à traiter sont très grandes (la plupart des cas, finalement), le choix n'est pas a faire. Le Xeon phi ne possédant que 16 Go de mémoire, toute la mémoire utilisée pour stocker les données sur le disque virtuel sera de la mémoire vive en moins pour l’exécution du programme.

Exemple :

icc -O3 -mmic program.c -o program

scp program mic0:

ssh mic0

./program